EMV-optimiertes Leiterplattendesign: Grundlagen, Maßnahmen und Praxistipps

Kernelemente elektrischer und elektronischer Geräte sind Leiterplatten. Sie übernehmen zentrale Funktionen wie Datenverarbeitung, Steuerung und Regelung und enthalten sowohl digitale Komponenten (z.B. Prozessoren, Speicherbausteine, FPGAs, ADCs, Displays, Kommunikationsbausteine) als auch analoge Schaltungsteile (z.B. OPVs, Schutzdioden, Filterelemente).

Die funktionalen Elemente der Leiterplatte sind sowohl Quelle unerwünschter elektromagnetischer Emissionen als auch Senke von Störphänomenen. Begleitende Design-Maßnahmen auf Geräteebene - wie Filterung, Schirmung oder optimiertes Kabeldesign - können die EMV-Eigenschaften wesentlich verbessern. Diese Maßnahmen sind jedoch oft kostenintensiv und führen nicht immer zum gewünschten Erfolg.

Unser Webinar vermittelt einen kompakten Überblick über wesentliche Designelemente und Maßnahmen, die zur Optimierung der EMV-Eigenschaften der Leiterplatte und damit der Quelle und der Störsenke führen.

Warum EMV-konformes Design wichtig ist

Elektrische Geräte müssen in allen Märkten bestimmte Grenzwerte der Störemission (leitungsgeführt, gestrahlt) einhalten, um eine rechtskonforme Vermarktung zu ermöglichen. Zudem bestehen in vielen Wirtschaftszonen, etwa in der Europäischen Union, auch gesetzlich verpflichtende Anforderungen an die Störfestigkeit (risikobasiert).

Die EMV sollte daher als entscheidendes Leistungsmerkmal betrachtet werden, das bereits früh in der Produktentwicklung berücksichtigt werden muss. Nur so lassen sich gesetzliche und normative Anforderungen zuverlässig erfüllen und nachweisen (Konformitätsbewertung für den Zielmarkt, ggf. behördliche Zulassungsverfahren).

Inhalte des Webinars

Grundlagen

- Differential Mode versus Common Mode

- Nahfeld > Antenne > Fernfeld

- Zeitbereich versus Frequenzbereich

Wesentliche Aspekte des EMV gerechten Designs

- Return Current

- Layer Stackup - Placement - Routing - Signal Integrity - Power Integrity

Weitere Informationen zum Webinar

- Teilnahmegebühr: kostenfrei

- Sprache: Deutsch

- Zielgruppe: Hardware-Entwickler (Stromlauf / Leiterplattenlayout / Gerätedesign)

Melden Sie sich jetzt für unser Webinar an!

Referenten

|

|

|

|

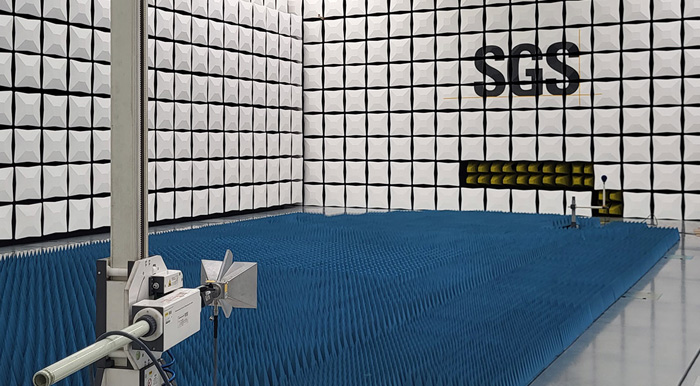

Karl-Heinz Schraink Karl-Heinz Schraink ist Ingenieur für Nachrichtentechnik (heute: Elektrotechnik mit Schwerpunkt Informationstechnik) und Kaufmann der Wirtschaftswissenschaften. Er hat vor 30 Jahren im heutigen SGS EMV Labor unterschiedlichste Geräte hinsichtlich der EMV bewertet (Messtechnik) und ist seit 30 Jahren im EMV Bereich tätig. Er war im Bereich Elektronikentwicklung von Kommunikationssystemen und Funkanlagen eines Großunternehmens in leitender Funktion für ein Labor / eine Entwicklungsdienststelle mit Schwerpunkt EMV, elektrische Sicherheit, Systementwärmung zuständig. Kernelement seiner Aufgabe war es nicht nur die EMV und Sicherheitseigenschaften der entwickelten Produkte normenkonform nachzuweisen, sondern auch frühzeitig durch die erforderlichen Maßnahmen im Design der Leiterplatte und auf System-/Geräteebene sicherzustellen, dass die gesetzlichen Anforderungen für den jeweiligen Zielmarkt möglichst ohne Redesing eingehalten werden können. |

Josef Bauer Dipl. Ing. (FH) Josef Bauer studierte Elektrotechnik an der FH München. Ab 1991 arbeitete er bei der Siemens AG in München als Prüfingenieur im Labor Überspannungs- und Störschutztechnik. Ab 2001 übernahm er die Leitung des akkreditierten EMV-Labors in diesem Bereich, das 2008 als 3rd Party-Labor zur SGS Germany GmbH integriert wurde. Neben seinen Tätigkeiten als EMV-Laborleiter ist er seit vielen Jahren Mitglied in diversen DKE-Normengremien, unter anderem im DKE/UK 811.2 „Elektromagnetische Verträglichkeit medizinischer elektrischer Geräte und/oder Systeme“.

|